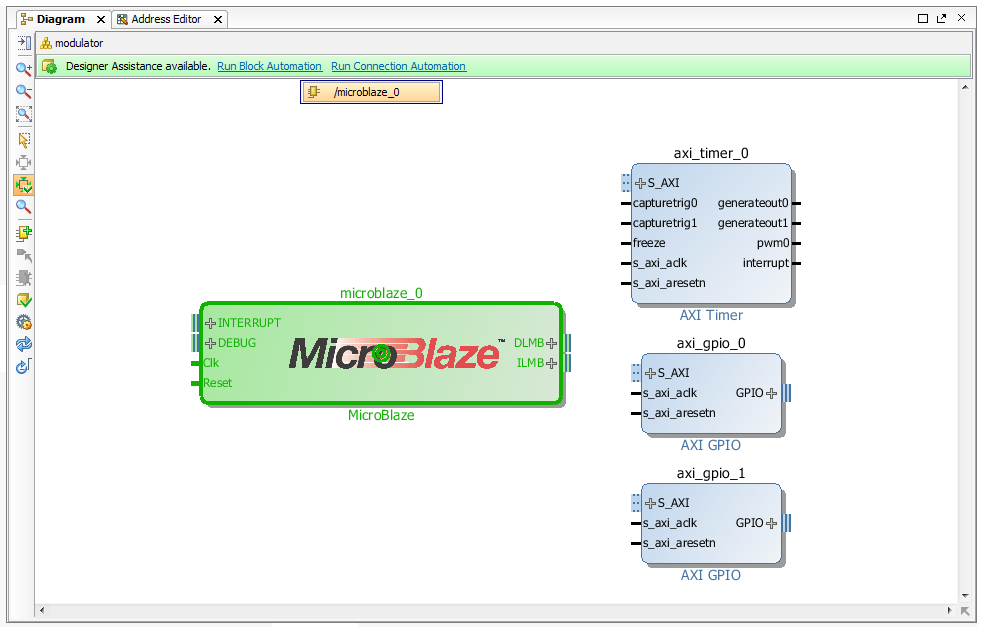

Analog signal processing on FPGA #2 - Integration of the MicroBlaze IP core into the FPGA - Blog - Summer of FPGA - element14 Community

Analog signal processing on FPGA #2 - Integration of the MicroBlaze IP core into the FPGA - Blog - Summer of FPGA - element14 Community

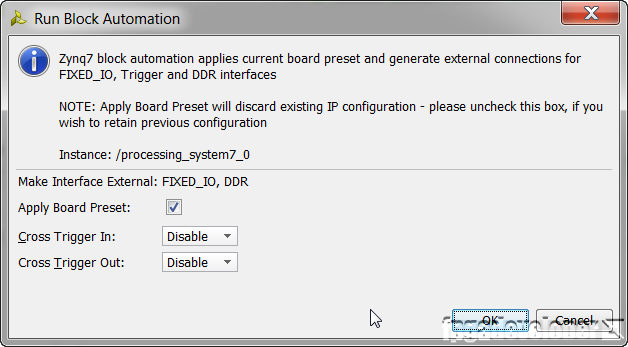

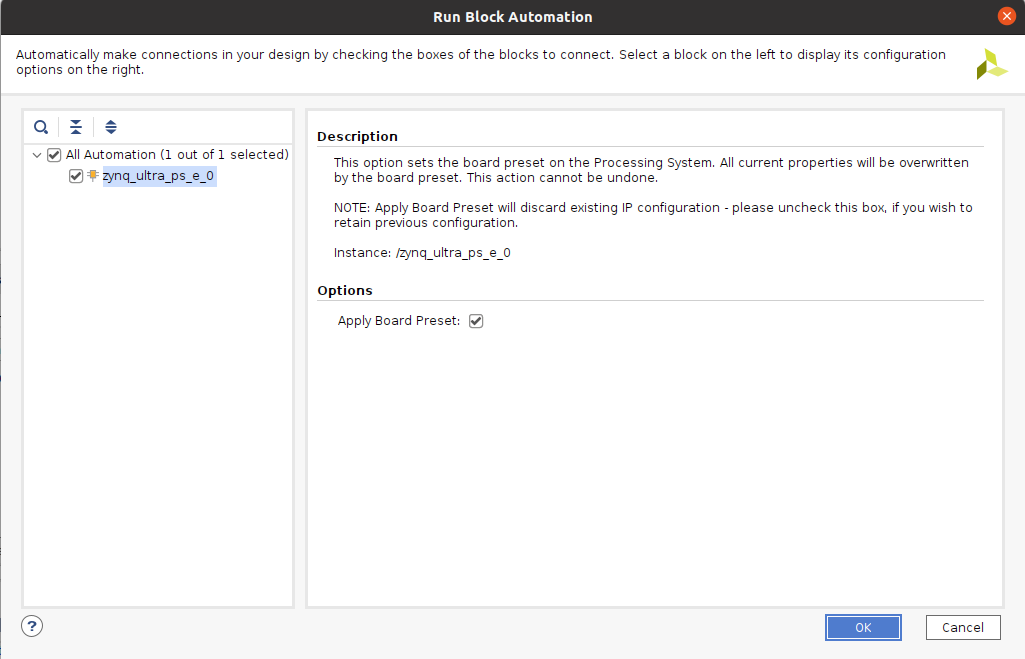

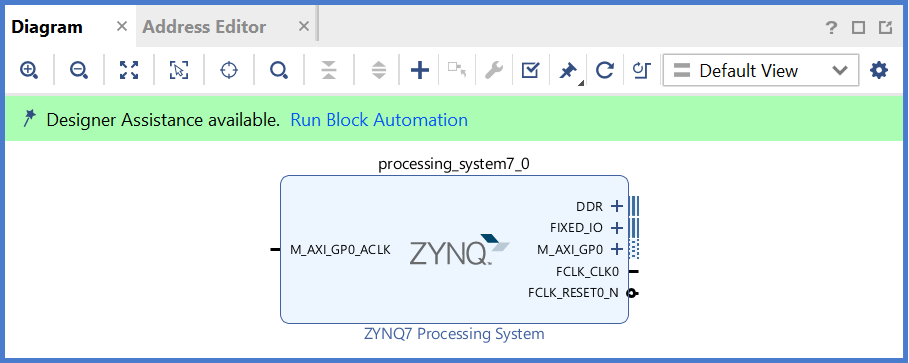

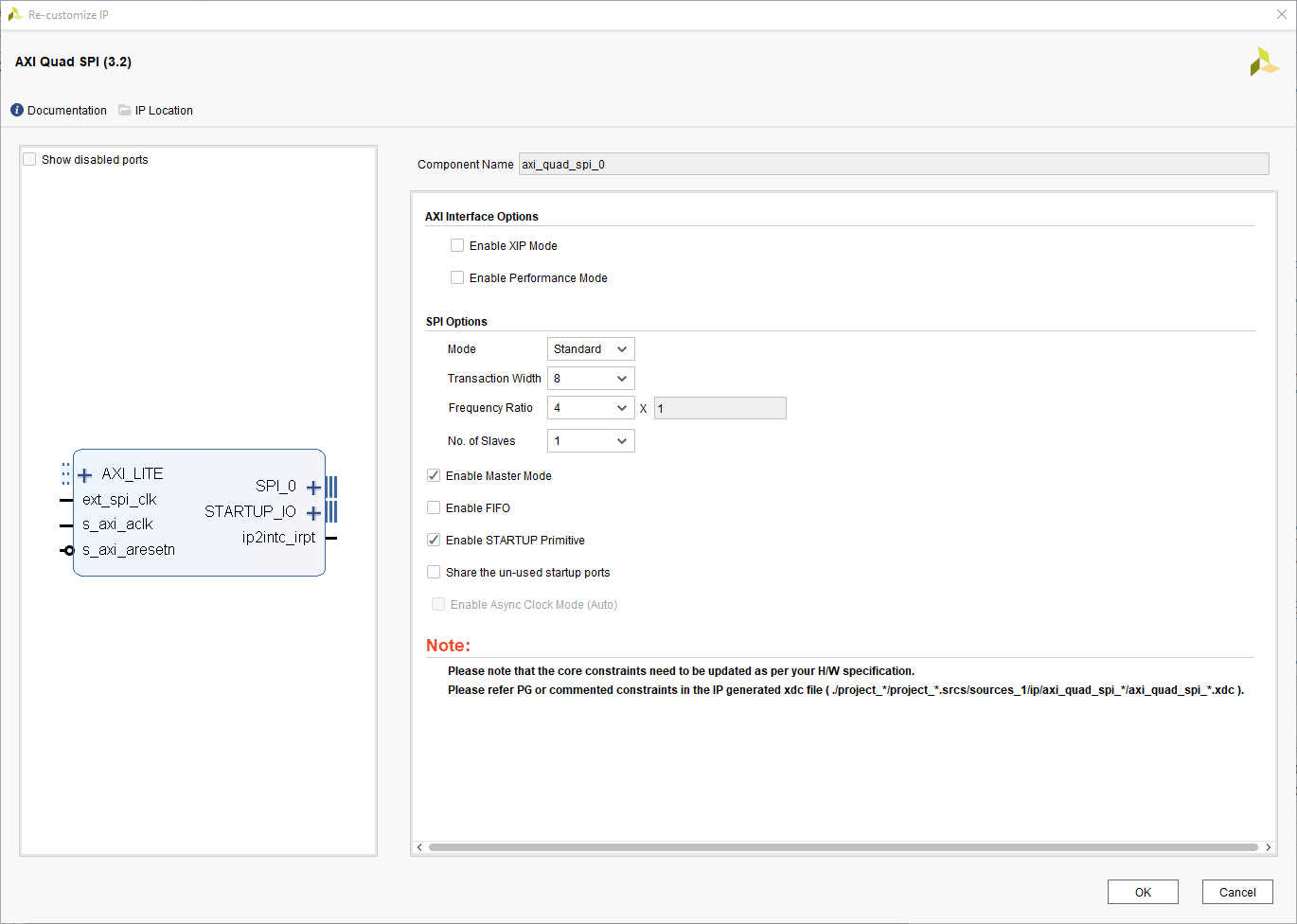

Mimas A7 Mini, MicroBlaze And Linux: How To Boot Linux On Mimas A7 Mini FPGA Development Board from SPI Flash | Numato Lab Help Center

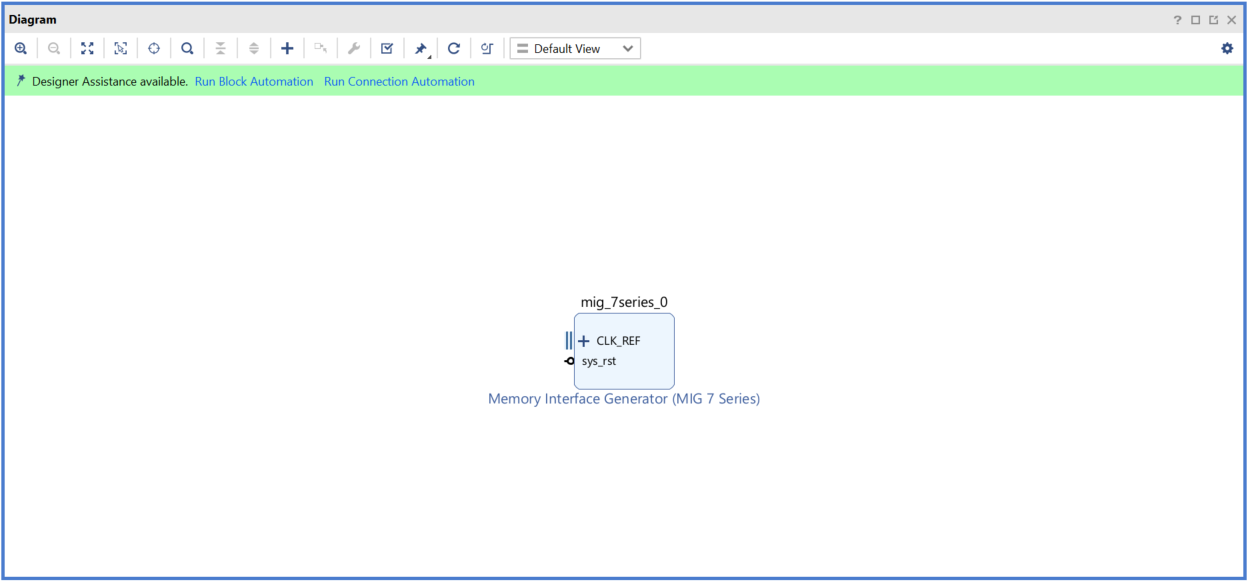

AXI 1G/2.5G Ethernet Subsystem ERROR when running Block Automation: [BD 41-2168] Errors found in procedure apply_rule:key "rst_polarity" not known in dictionary.